加倍監控伺服器的人工智慧效能

人工智慧 (AI) 與機器學習技術能為大規模監控系統添增巨大價值——例如智慧城市所部署的系統。 機器智慧能夠幫助緩解交通阻塞、監控重要地點並執行其他各式各樣的作業。

例如,行為分析即是 AI 型視訊監控新興的應用領域,讓監控系統「學習」其監控環境下典型的行動(例如人行道)並於發生異常事件時主動通報(例如車輛停到人行道時)。 再進一步則是事件導向監控,在發生一系列的行動時(例如有人於指定外的時間進入管制區域時)觸發回應(例如語音廣播警告侵入者已違法侵入)。

此類功能需要可觀的運算效能,這種效能傳統上僅可能從大型資料中心環境獲得。 這為系統營運商帶來一大挑戰,因為視訊串流會占用可觀的網路頻寬,造成高昂的傳輸成本。 特定的應用程式亦可能因為需視訊資料持續送往第三方資料中心而產生額外延遲,影響使用品質。

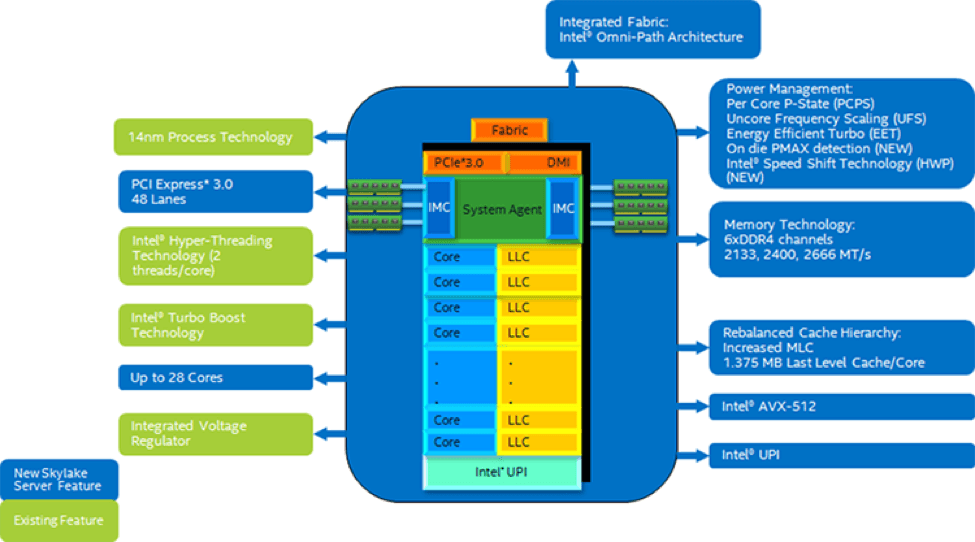

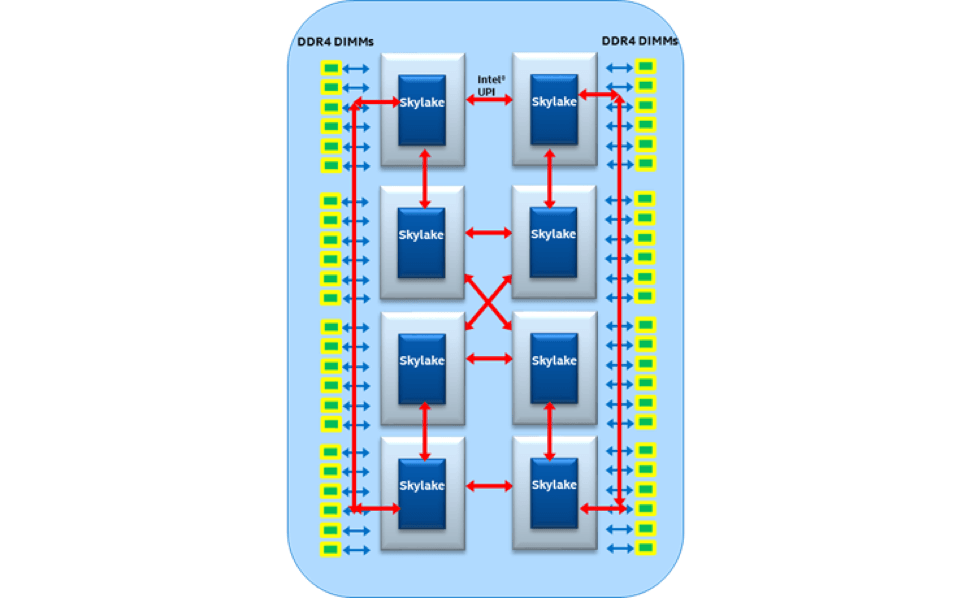

業者如需部署人工智慧監控系統,可考慮新的 Intel® Xeon® 可擴充系列產品(原代號為 Purley),能將 AI 工作負載效能提升一倍以上。 如圖 1 所示,此平台主要特色包括:

- 每插槽最高 28 個核心,較前代最高 24 個核心更加提升

- Intel® Advanced Vector Extensions 512 將矩陣數學輸送量加倍

- 新的網狀互連架構,能降低延遲並改善記憶體頻寬

- 新一代的 Intel® Omni-Path Architecture 交換架構技術可擴充規模至上萬個節點

簡而言之,Xeon® 可擴充系列產品能夠實現進階邊緣伺服器,滿足智慧城市不斷進化的需求。

圖 1. Intel® Xeon® 可擴充伺服器增強多項功能,改善數位安全與監控系統的視訊分析與 AI 工作負載效能。 (資料來源:Intel)

為接近邊緣的 AI 運算提供兩倍運算輸送量

效能升級就從每個插槽最高 28 個核心開始,在八插槽系統最多可配備 224 個核心,核心時脈速度則從每核心 1.9 GHz 到 3.6 GHz。 另外,每個核心並支援 Intel® AVX-512 SIMD 指令集。

雖然 Intel® AVX-512 指令集支援並非首次配備於 Intel® 處理器(最初於 Intel® Xeon Phi™ 產品線推出),但是因針對高效能運算工作負載而新開發數個 512 位元指令,其運算輸送量已達 Intel® AVX/AVX2 的兩倍。 而在監控應用方面,AVX512DQ 指令集更能增強視訊分析與 AI 應用常用的光跡追蹤、雙精度矩陣乘算、快速傅立葉轉換 (FFT) 及摺積工作負載中的整數和浮點數運算。

為支援這些進階指令,已將兩組融合乘加運算 (Fused Multiply-Add) 單元從 256 位元升級為 512 位元。 FMA 單元能改善複雜浮點運算的精度,將整個計算式以 a + b * c 的方式計算後,再無條件捨去至最接近的有效位元。 如此可提供較高解析度的結果供視訊分析等訊號處理應用使用,以及其他如摺積和深層神經網路(CNN 與 DNN)等需要累加多個輸入的程式使用。

新的 Intel® Xeon® 可擴充處理器與前一代相比,各方面的效能提升總計能為深度學習訓練與推斷運算帶來 2.2 倍的進步,是以 AI 技術為基礎的視訊分析關鍵。

網狀互連降低延遲,最大化數位安全與監控系統效能

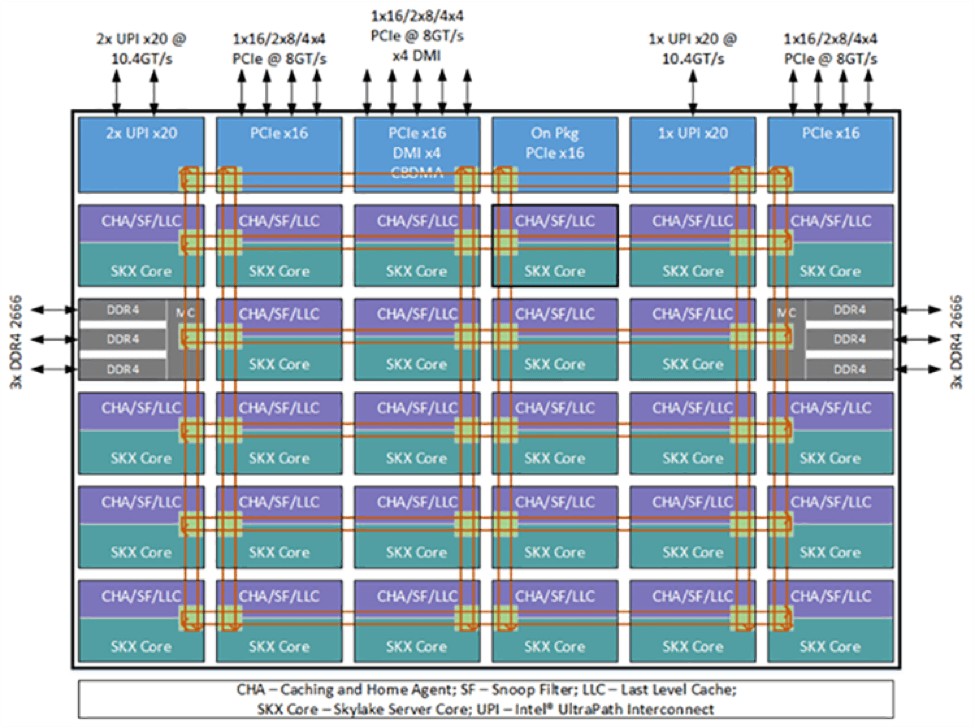

為最大化 Intel® Xeon 可擴充處理器增加的核心數量和其中整合式加速功能所帶來的效能,14 奈米製程的 Skylake-SP 微架構還配備了新的晶片網狀互連拓撲,降低核心對核心通訊的延遲。

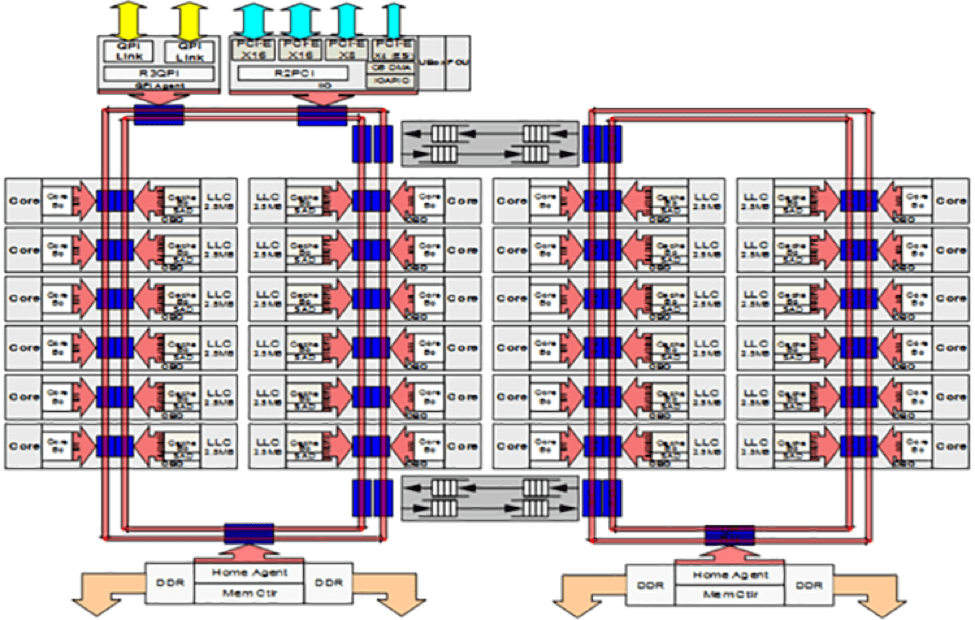

如圖 2A 和 2B 所示,網狀互連取代前一代微架構的環狀拓撲,讓通訊能夠經由最短的垂直或水平路徑進行。 網狀互連當中還整合了快取代理程式、本機代理程式以及 I/O 子系統,讓核心存取這些功能時仍可受益於較低延遲時間。

圖 2A. 前一代微架構的環狀互連在高輸送量系統可能導致效能瓶頸形成。 (資料來源:Intel)

圖 2B. Intel® Xeon® 可擴充處理器的網狀互連拓撲提供最短可能的通訊路徑,進而降低核心對核心的通訊延遲。 (資料來源:Intel)

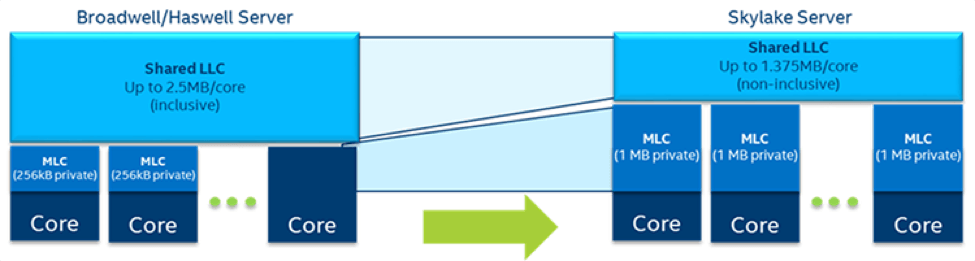

重新設計的快取記憶體階層結構也將 L1 快取記憶體加倍、增加 L2 快取記憶體至 1 MB,並將最後一階快取記憶體 (LLC) 減少至每個核心非包含式 1.375 MB 快取記憶體(圖 3)。 將較多快取記憶體重新配置到更接近核心的位置,降低了 Xeon® 可擴充處理器的記憶體存取延遲,而改用非包含式 LLC 則改善了整體記憶體利用率。

圖 3. 增加接近核心的快取記憶體容量使得 Intel® Xeon® 可擴充處理器的記憶體存取延遲比前代更低。 (資料來源:Intel)

由於監控應用的快取命中率高,因此這些功能最終改善記憶體頻寬 1.5 倍。 同時,記憶體效能更獲得六通道 2133 至 2666 MHz DDR4 SDRAM 以及每個 CPU 最高 1.5 TB 的記憶體容量支援。

擴充至百萬兆級

監控伺服器通常採用多晶片、多插槽系統,因此插槽間、機架間以及核心之間需要有高速、低延遲的通訊能力。

在晶片對晶片的通訊方面,Intel® Xeon® 可擴充處理器提供可觀的高速 I/O 增強功能,包括每個 CPU 共 48 線 PCIe 3.0 線道、最多 14 個 SATA3 連接埠、10 個 USB 3.0 連接埠以及整合式 Intel® Ethernet Connection X722。

但是為使多插槽通訊符合 Intel® Xeon® 可擴充處理器的增強效能,其 Intel® QuickPath Interconnect 則由每個處理器二至三組的 Intel® Ultra-Path Interconnect 取代。 Intel® Ultra-Path Interconnect 是一套具備一致性的互連技術,提供 10.4 GTps 的插槽對插槽資料傳輸速率,並於每一個核心及 LLC 排內建分散式合併快取暨本機代理程式 (CHA) 以提升可擴充性(圖 4)。

圖 4. Intel® Ultra-Path Interconnect 是具備快取一致性的插槽對插槽互連技術,能夠提供 10.4 GTps 的資料傳輸速率。

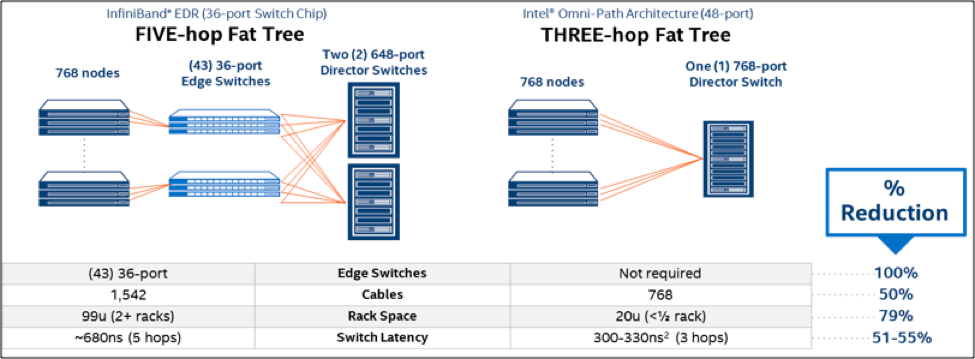

除了單一系統外,Intel® Xeon® 可擴充處理器亦支援 Intel® Omni-Path Architecture。這是 Intel® True Scale Fabric 與 InfiniBand 的後繼技術,價格具競爭力、提供 100 Gbps 的連線速率,且可支援擴充至超過 10,000 個節點。

Intel® Omni-Path Architecture 的重要性在於能夠減少支援百萬兆級運算所需的硬體,同時仍維持舊型交換技術的軟體相容性。 將自適應/離散式路由、流量最佳化、動態線道擴充、封包完整性保護等功能整合於單一技術,即無需再配備邊緣交換器,且可減少機架空間需求並將纜線數量減半,如此即可 節省可觀成本和維護所需(圖 5)。

圖 5 | 除了提供能夠支援逾 10,000 個節點的基礎架構,Intel® Omni-Path Architecture 亦減少百萬兆級運算部署所需的硬體。

Intel® Omni-Path Architecture 技術整合於特定 Intel® Xeon 可擴充處理器 SKU 中,或可透過擴充卡導入,能夠直接插接於監控伺服器系統。

監控伺服器建構模塊

目前在嵌入式及網路設備市場的原始設備製造商 (OEM) 已開始提供以 Intel® Xeon® 可擴充處理器為基礎的數位安全與監控系統的伺服器解決方案。

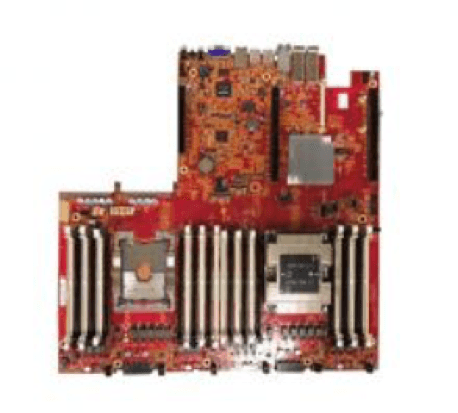

EnnoconnNSB-1021 即為一例。這是一款整合式網路主機板,支援最多兩個 24 核心 Intel® Xeon® 可擴充處理器、兩個 Intel® C620 系列輔助晶片組、每個 CPU 最多 48 個 PCI Express 3.0 線道、六通道的高速 DDR4 SDRAM,且散熱設計功率 (TDP) 僅有 70 W(圖 6)。

圖 6. Ennoconn NSB-1021 是邊緣伺服器開發極佳的出發點。 (資料來源:Ennoconn)

因為有了 Intel® Xeon® 可擴充處理器的泛用性與 Intel® Ultra-Path Interconnect 和 Intel® Omni-Path Architecture 等功能,監控系統開發人員能夠從 NSB-1021 各種版本著手針對目標價格與每瓦效能進行開發,然後視需求增加而擴充規模至多排本地化的伺服器陣列。

用 Intel® Xeon® 可擴充處理器實現智慧監控

隨著監控系統為了滿足智慧城市的需求而開始整合 AI 技術等先進技術,降低網路傳輸成本和通訊延遲是兩個必須妥善解決的問題。 一個能夠同時解決兩方面問題的方法,即是透過能夠執行視訊分析運算的監控伺服器,將伺服器部署於接近視訊來源之處。

雖然進階視訊分析與 AI 工作負載一向僅能夠於資料中心執行,新的 Intel® Xeon® 可擴充處理器為監控系統及智慧城市營運商提供了另一種選擇,將智慧功能推往網路邊緣。 這使得監控系統變得更聰明。